Product Summary

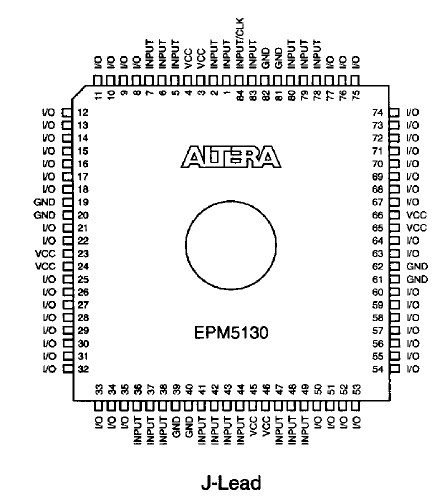

The EPM5130GC is an Erasable Programmable Logic Device. The EPM5130GC is a user-configurable, high-performance Multiple Array Matrix (MAX) 5000-family EPLD that is optimized for pinintensive designs. It provides a high-density replacement for 7400-series SSI and MSI TTL and CMOS logic. The EPM5130GC is available in windowed ceramic 84-pin J-Iead chip carrier (JLCC), 100-pin pin-grid array (PGA), and 100-pin quad flat pack (WQFP) packages, as well as OIP plastic J-Iead (PLCC) and QFP packages. A single EPM5130GC can quickly integrate multiple 20- and 24-pin low-density PLDs and high-pin-count subsystems, such as custom DMA controllers. In addition, it can handle a 32-bit data path application with enough I/O to allow the required control signals to be implemented.

Parametrics

EPM5130GC absolute maximum ratings: (1)Supply voltage : -2.0 to 7.0 V; (2)Programming supply voltage : -2.0 to 13.5 V; (3)DC input voltage : -2.0 to 7.0 V; (4)DC VCC or GND current : 500 mA; (5)DC output current, per pin : -25 to 25 mA; (6)Power dissipation : 2500 mW; (7)Storage temperature : -65 to 150 ℃; (8)Ambient temperature : -65 to 135 ℃; (9)Junction temperature : 150 ℃.

Features

EPM5130GC features: (1)High-density 128-macrocell general-purpose MAX 5000 EPLD; (2)128 macrocells optimized for pin-intensive applications, easily integrating over 60 TTL MSI and SSI components; (3)High pin count for 16- or 32-bit data paths; (4)20 high-speed dedicated inputs for fast latching of 16-bit functions; (5)Fast clock-to-output delays for bus-oriented functions; (6)Programmable I/O architecture that allows up to 84 inputs or 64 outputs in windowed ceramic PGA, and windowed ceramic and onetime-programmable (OTP) plastic QFP packages; (7)Programmable I/O architecture that allows up to 68 inputs or 48 outputs in windowed ceramic and plastic OTP J-lead packages.

Diagrams

(China (Mainland))

(China (Mainland))