Product Summary

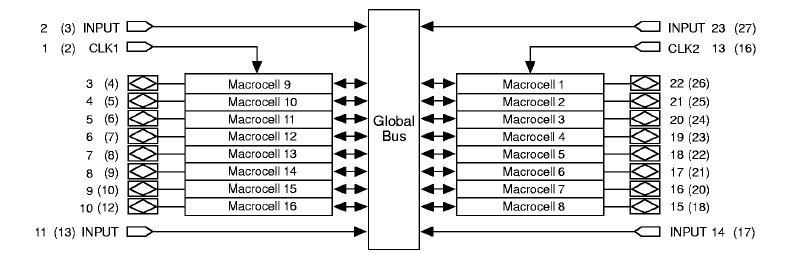

The EP610DI-30 is an Erasable Programmable Logic Device. The EP610DI-30 has 16 macrocells, 4 dedicated input pins, 16 I/O pins, and 2 global clock pins (see Figure 8). Each macrocell can access signals from the global bus, which consists of the true and complement forms of the dedicated inputs and the true and complement forms of either the output of the macrocell or the I/O input. The CLKl signal is a dedicated global clock input for the registers in macrocells 9 through 16. The CLK2 signal is a dedicated global clock input for registers in macrocells 1 through 8.

Parametrics

EP610DI-30 absolute maximum ratings: (1)Supply voltage : -2.0 to 7.0 V; (2)DC input voltage : -2.0 to 7.0 V; (3)DC VCC or ground current : -175 to 175 mA; (4)DC output current, per pin : -25 to 25 mA; (5)Storage temperature : -65 to 150 ℃; (6)Ambient temperature : -65 to 135 ℃; (7)Junction temperature : 135 ℃.

Features

EP610DI-30 features: (1)Programmable I/O architecture with up to 20 inputs or 16 outputs and 2 clock pins; (2)EP610 and EP6101 devices that are pin-, function-, and programming file-compatible; (3)Programmable clock option for independent clocking of all registers; (4)Macrocells individually programmable as 0, T, JK, or SR flipflops, or for combinatorial operation.

Diagrams

(China (Mainland))

(China (Mainland))