Product Summary

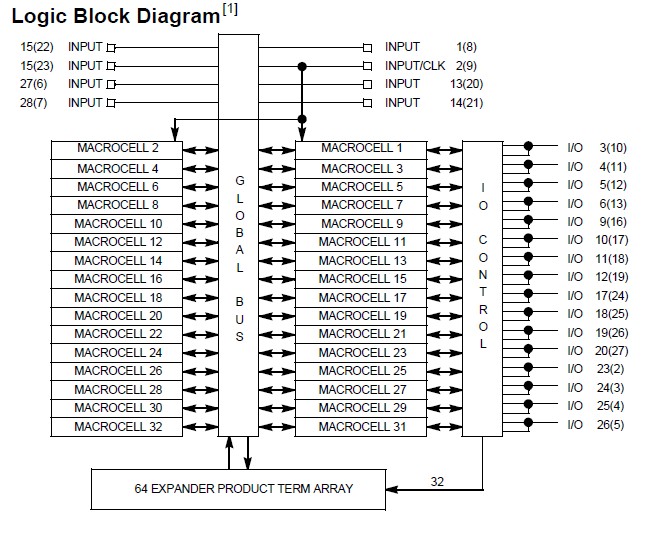

The CY7C344-25WMB is a 32-Macrocell MAX EPLD. Available in a 28-pin, 300-mil DIP or windowed J-leaded ceramic chip carrier (HLCC), the CY7C344-25WMB represents the densest EPLD of this size. Eight dedicated inputs and 16 bidirectional I/O pins communicate to one logic array block. In the CY7C344-25WMB LAB there are 32 macrocells and 64 expander product terms. When an I/O macrocell is used as an input, two expanders are used to create an input path. Even if all of the I/O pins are driven by macrocell registers, there are still 16 “buried” registers available. All inputs, macrocells, and I/O pins are interconnected within the LAB.

Parametrics

CY7C344-25WMB absolute maximum ratings: (1)Storage Temperature:–65 to +150℃; (2)Ambient Temperature with Power Applied: 0 to +70℃; (3)Maximum Junction Temperature (Under Bias): 150°C; (4)Supply Voltage to Ground Potential: –2.0V to +7.0V; (5)Maximum Power Dissipation: 1500 mW; (6)DC VCC or GND Current: 500mA; (7)DC Output Current, per Pin:–25 mA to +25mA; (8)DC Input Voltage[2]:–3.0V to +7.0V; (9)DC Program Voltage: +13.0V.

Features

CY7C344-25WMB features: (1)High-performance, high-density replacement for TTL, 74HC, and custom logic; (2)32 macrocells, 64 expander product terms in one LAB; (3)8 dedicated inputs, 16 I/O pins; (4)0.8-micron double-metal CMOS EPROM technology; (5)28-pin, 300-mil DIP, cerDIP or 28-pin HLCC, PLCC package.

Diagrams

(China (Mainland))

(China (Mainland))